摩爾定律失效,芯片性能提升遇瓶頸

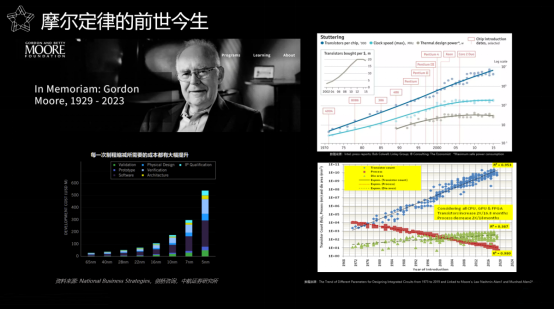

在探讨Chiplet(小(xiǎo)芯片)之前,摩爾定律是繞不開(kāi)的話(huà)題。戈登·摩爾先生(shēng)在1965 年提出了摩爾定律:每年單位面積内的晶體(tǐ)管數量會增加一(yī)倍,性能也會提升一(yī)倍。這意味着,在相同價格的基礎上,能獲得的晶體(tǐ)管數量翻倍。不過,摩爾先生(shēng)在十年後的1975年,把定律的周期修正爲24個月。至此,摩爾定律已經影響半導體(tǐ)行業有半個世紀。

随着集成電(diàn)路技術的不斷演進,半導體(tǐ)行業發現摩爾定律在逐漸失效。上圖右上部分(fēn)是英特爾x86 CPU 1970-2025年的演化曆史,可看出每顆芯片的晶體(tǐ)管數量持續增加(右上深藍(lán)色線條),但時鍾速度(右上天藍(lán)色線條)和熱設計功耗(右上灰色線條)自2005年之後就變化不大(dà)。于此同時,受先進工(gōng)藝高成本支出的影響,晶體(tǐ)管成本降幅在2012年後趨緩,甚至越往後還有成本增加的趨勢。

從上圖右下(xià)的統計數據可看出,芯片制程在持續微縮和演進,晶體(tǐ)管數也在相應的增長。在2019年以前,單芯片晶體(tǐ)管數量和工(gōng)藝幾何尺寸演進,一(yī)直與摩爾定律高度相關。因爲單位面積内的晶體(tǐ)管數量,每一(yī)周期就會增加一(yī)倍,所以在理想情況下(xià),Die的尺寸可保持不變。但是據右下(xià)綠色标識的區域顯示,可以看到單芯片Die尺寸在日趨增大(dà),這也從另一(yī)個角度說明,單芯片晶體(tǐ)管數量的增加,也有Die增大(dà)的原因所緻。由于Die尺寸的增長,受光罩尺寸、工(gōng)藝良率等因素制約,這代表通過加大(dà)Die Size來提升單芯片算力已經越來越困難。

總而言之,随着集成電(diàn)路技術的發展和演進,每24個月已經很難讓單位面積内的晶體(tǐ)管數量翻倍。這意味着,現在芯片性能的提升遭遇了瓶頸,性能無法單純由工(gōng)藝技術驅動,也需要由架構創新來驅動。因此,業界必須找到新的解決方案。

Chiplet幫助芯片生(shēng)産降本增效

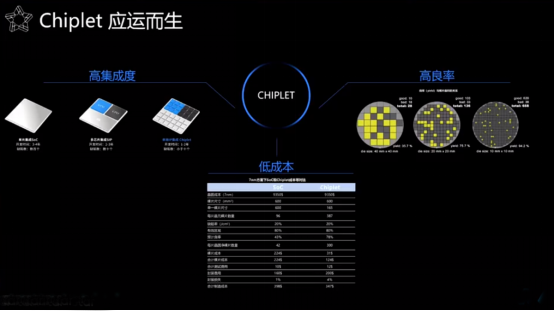

在摩爾定律逐漸失效的情況下(xià),Chiplet技術在半導體(tǐ)行業應運而生(shēng)。整體(tǐ)來看,Chiplet具備高集成度、高良率、低成本三大(dà)特點,它被視爲延續摩爾定律的關鍵技術。

Chiplet通過多個芯片的片間集成,可以突破傳統單芯片的上限,進一(yī)步提高芯片的集成度。比如,左上圖的單片集成的SoC是通過統一(yī)工(gōng)藝制程,導緻芯片上各個部分(fēn)都要同步進行叠代,其開(kāi)發時間長達三至四年,缺陷數量可達數百個。左上圖的單獨IP集成Chiplet通過将不同的功能切開(kāi),再對部分(fēn)單元的工(gōng)藝做選擇性叠代,叠代裸片後可制造出下(xià)一(yī)代産品,這樣就能加速産品的上市周期。Chiplet芯片集成應用較爲廣泛和成熟的裸片,就有效降低了Chiplet芯片研制風險,也減少了重新流片和封裝的次數,進而能爲芯片企業節省研發投入。

Chiplet可以提升複雜(zá)SoC芯片的良率,該方案将複雜(zá)SoC芯片分(fēn)成更小(xiǎo)的芯片。單芯片的面積越大(dà)其良率越低,它對應的芯片制造成本也就越高,芯片設計成本也會随着制程的演進而成本增長,切割小(xiǎo)芯片可有效降低芯片設計成本。此外(wài),在SoC設計中(zhōng),模拟電(diàn)路、大(dà)功率IO對制程并不敏感,不需要太高端的芯片制程,可将SoC中(zhōng)的功能模塊,劃分(fēn)成單獨的Chiplet,針對功能來選擇合适的制程,從而讓芯片實現最小(xiǎo)化,提高芯片的良率、降低芯片成本。

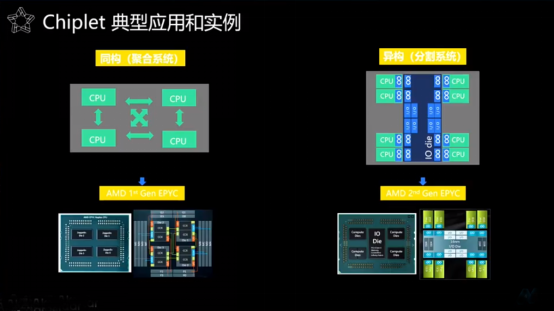

Chiplet有兩個常見的應用案例:同構(聚合系統)和異構(分(fēn)割系統)。同構是通過高速接口和先進的封裝技術,适用于CPU、TPU、AI SoC等,這種方式是将多個Die緊密相連,以相同的Die設計實現計算能力的擴展,其接口要求低延遲和低誤碼率;異構是将芯片按功能拆分(fēn),先進制程的Die提供高算力和性能,成熟制程的Die負責常規或者特色的功能,這些不同制程的Die被封裝在一(yī)起。

在使用案例方面,AMD服務器CPU Epyc系列的第一(yī)代和第二代,分(fēn)别采用了同構和異構的方法。第一(yī)代Epyc采用7nm制程,利用同構方法聚合4個相同的Die,該系統可擴展,隻需多個Die的互聯,即可提高計算能力;第二代 Epyc将芯片功能拆分(fēn)爲CCD運算Die(Compute Core Die)和IO Die,通過異構方法它們集成到一(yī)起,實現了先進工(gōng)藝與成熟工(gōng)藝的巧妙融合。

通過高速接口和先進封裝技術,把多顆Die融合在一(yī)顆大(dà)芯片内,以此來實現算力的擴展,這适用于CPU、FPGA、通信芯片等産品。同時,Chiplet也對接口提出了标準化、兼容性、可移植性的要求,要具備低延時和低誤碼率的優勢,廠商(shāng)選擇接口時還需考慮生(shēng)态系統問題。

曾克強總結說:“Chiplet可提升大(dà)芯片設計良率,降低芯片研發的風險,縮短芯片的上市時間,還可增加芯片産品組合,延長産品生(shēng)命周期。因此,它被視爲有效延續摩爾定律的新方式。”

Chiplet的發展趨勢及生(shēng)态布局

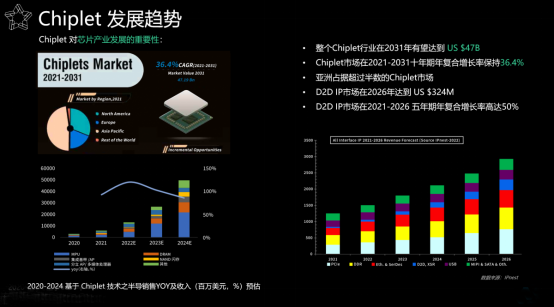

Chiplet應用在芯片中(zhōng)的時間還不長,但自2020年開(kāi)始其發展就非常快,年複合增長率達到36.4%。預測到2031年,全球Chiplet行業市值有望達到470億美元(下(xià)圖左邊)。

因爲Chiplet把芯片切分(fēn)成不同的小(xiǎo)芯片并互聯,所以相關接口IP市場也有新的需求。上圖右邊是各類傳統接口IP市場的發展趨勢,藍(lán)色方塊體(tǐ)現了小(xiǎo)芯片互聯接口IP的趨勢。雖然小(xiǎo)芯片互聯接口IP的發展時間較短,但是其增長速度最爲迅猛,預計從2021年到2026年,年複合增長率會高達50%。至2026年,全球産值将達3.2億美元。

Chiplet技術需要切分(fēn)、堆疊整合,該技術将推動芯片産業鏈的變革。曾克強預測,Chiplet的發展将分(fēn)爲幾個階段:2023年之前的兩三年是Chiplet生(shēng)态早期階段,芯片公司對芯片進行分(fēn)拆,并尋找先進封裝組合,各家都按自己的定義協議來做産品,該階段并未形成統一(yī)的标準。

進入到2023年,随着工(gōng)藝制程進入3納米接近物(wù)理極限,摩爾定律失效越來越明顯,而摩爾先生(shēng)的去(qù)世,似乎也在印證舊(jiù)時代正在落幕。與此同時,屬于Chiplet的新時代正在開(kāi)啓。設計廠商(shāng)對自己設計的Chiplet進行自重用和自叠代,同時工(gōng)藝逐漸成型,互聯标準日趨統一(yī)。

預計到2027年,Chiplet生(shēng)态将進入成熟期,真正進入IP硬化時代。屆時,會誕生(shēng)一(yī)批新公司:Chiplet小(xiǎo)芯片設計公司、集成小(xiǎo)芯片的大(dà)芯片設計公司、有源基闆供應商(shāng)、支持集成Chiplet的EDA公司。

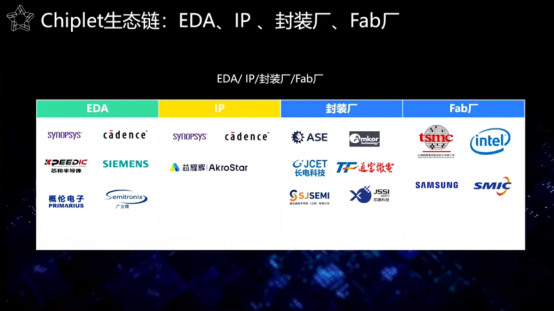

主要有四個重要角色參與Chiplet生(shēng)态鏈:EDA供應商(shāng),IP廠商(shāng),封裝廠,Fab廠。尤其對于IP供應商(shāng)而言,基于IP複用的模式,設計能力較強的IP供應商(shāng)有潛力演變爲Chiplet供應商(shāng)。而IP供應商(shāng)也需要具備高端芯片的設計能力,以及多品類的IP布局和平台化的運作能力,以上都對IP供應商(shāng)提出了更高的要求。又(yòu)由于Chiplet加入了更多的異構芯片和各類總線,相應的EDA覆蓋工(gōng)作就變得更加複雜(zá),需要更多的創新功能。國内EDA企業需要提升相關技術,應對堆疊設計帶來的諸多挑戰,例如對熱應力、布線、散熱、電(diàn)池幹擾等的精确仿真,在封裝方面需要2.5D和3D先進封裝技術支持,同時Fab方面也需要相關技術的支持。

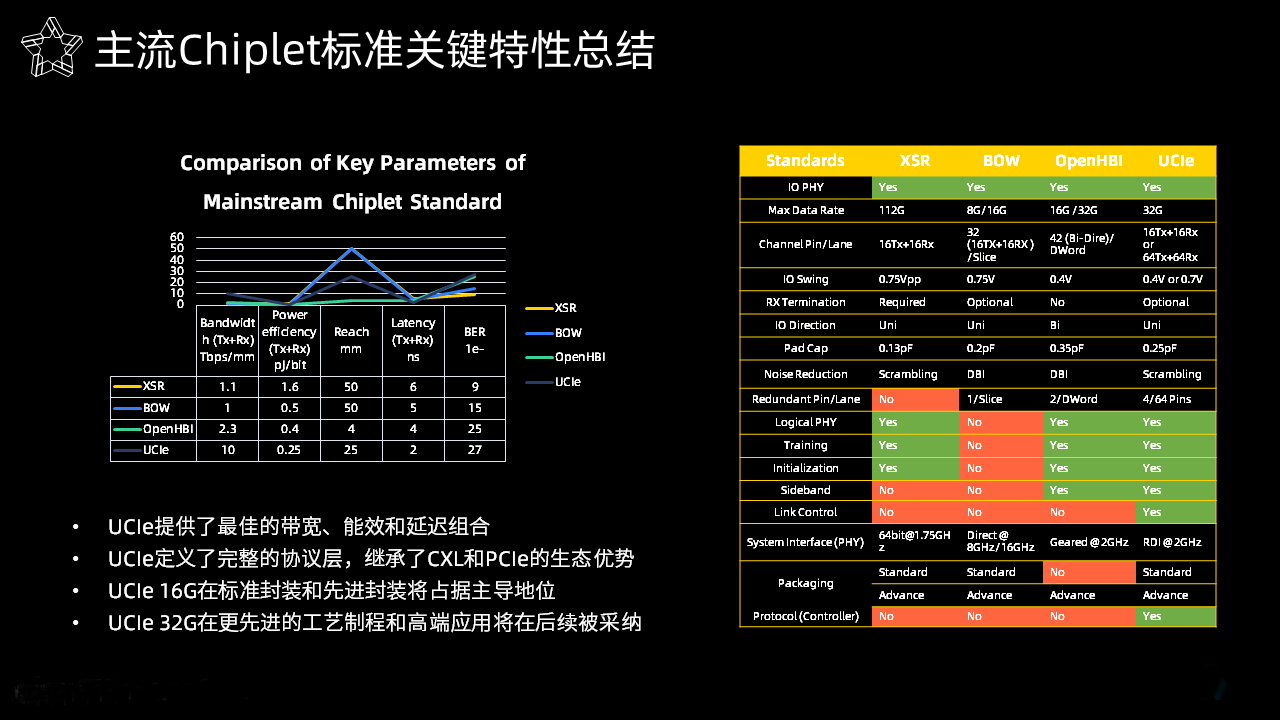

經過了幾年的發展,國際上出現了一(yī)些Chiplet标準,主流标準包括XSR、BOW、OpenHBI、UCIe(詳見上圖右表)。右表中(zhōng)的綠色代表技術優勢,紅色代表劣勢。可以看出UCIe标準在多個角度都占據優勢,它定義了邏輯 PHY、訓練機制、初始化序列、邊帶和鏈路控制。此外(wài),它還重用了成熟的PCIe和CXL生(shēng)态系統,這将加快這一(yī)新标準的采納,并得到代工(gōng)廠、封裝廠、無晶圓廠和系統公司的支持。

從左側的圖表中(zhōng)可以看出,UCIe提供了最高帶寬、最佳能效比和最低延遲的最佳組合。具體(tǐ)來看,UCIe定義了完整的協議層,繼承了CXL和PCIe生(shēng)态系統的優勢。UCIe 16G将主導标準封裝和先進封裝行業,UCIe 32G将在更先進封裝工(gōng)藝和高端應用方面将被采納。

如何解決Chiplet面臨的挑戰

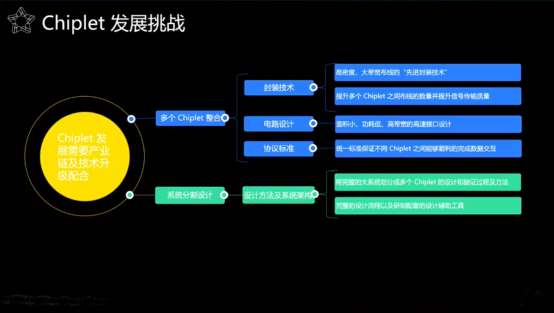

Chiplet的發展剛起步不久,還面臨着非常多的挑戰,它需要産業鏈及技術升級配合。這些挑戰主要分(fēn)爲兩大(dà)類:上圖藍(lán)色部分(fēn)展示的是多個Chiplet堆疊整合的挑戰,綠色部分(fēn)是怎麽系統分(fēn)割設計方面的挑戰。

堆疊整合往下(xià)還細分(fēn)爲封裝技術、電(diàn)路設計、協議标準三方面的挑戰。

首先,Chiplet技術把單個大(dà)矽片“切”成多個小(xiǎo)芯片,再把這些小(xiǎo)芯片封裝在一(yī)起,單顆矽片上的布線密度和信号傳輸質量遠高于不同小(xiǎo)芯片,這就要求必須要發展出高密度、大(dà)帶寬布線的先進封裝技術,盡可能提升在多個Chiplet之間布線的數量并提升信号傳輸質量。Intel和台積電(diàn)都已經有了相關的技術儲備,通過中(zhōng)介層(Interposer)将多個Chiplet互連起來,目前這些技術仍在不斷演進中(zhōng),并在不斷推出更新的技術。

其次,用于Chiplet之間的高速通信接口電(diàn)路設計。Chiplet之間的通信雖然可以依靠傳統的高速Serdes電(diàn)路來解決,甚至能完整複用PCIe這類成熟協議。但這些協議主要用于解決芯片間甚至闆卡間的通信,在Chiplet之間通信用會造成面積和功耗的浪費(fèi)。

再次,通信協議是決定Chiplet能否“複用”的前提條件。Intel公司推出了AIB協議、TSMC和Arm合作推出LIPINCON協議,但在目前Chiplet仍是頭部半導體(tǐ)公司才會采用的技術,這些廠商(shāng)缺乏與别的Chiplet互聯互通的動力。目前,UCIe聯盟最重視協議,如果實現了通信協議的統一(yī),IP公司就有可能實現從“賣IP”到“賣Chiplet”的轉型。

先進封裝解決了如何“拼”的問題,更重要的是要解決如何“切”的問題。英偉達在決策下(xià)一(yī)代GPU要采用Chiplet技術時,思考和驗證如何把完整的大(dà)芯片設計劃分(fēn)成多個Chiplet,這其實是設計方法學的初步體(tǐ)現。要讓基于Chiplet的設計方法從“可用”變爲“好用”,需要定義完整的設計流程,以及研制配套的設計輔助工(gōng)具。

在中(zhōng)國發展Chiplet面臨哪些挑戰?從技術上面看來,中(zhōng)國現在産業鏈發展最大(dà)的挑戰是技術封鎖,由封鎖所帶來的自主需求也是一(yī)大(dà)機遇。在單位矽片面積上增加晶體(tǐ)管數量有困難,轉而追求在單個封裝内部持續提升晶體(tǐ)管數,這也是目前發展Chiplet技術對國内芯片産業的最大(dà)意義。

但是現在我(wǒ)們仍缺乏必要技術、經驗、标準協議、人才、知(zhī)識産權和專利積累,而且中(zhōng)國芯片公司的規模都不大(dà),無法單靠某一(yī)家或某幾家公司來打造Chiplet生(shēng)态。這需要不同的公司分(fēn)工(gōng)合作,共同打造Chiplet産業鏈。

中(zhōng)國要發展自己的Chiplet生(shēng)态鏈就需要有自己的标準。國内的CCITA聯合集成電(diàn)路企業和專家,共同主導定義了小(xiǎo)芯片接口總線技術要求,這是中(zhōng)國首個原生(shēng)Chiplet标準,在去(qù)年12月15日通過了工(gōng)信部電(diàn)子工(gōng)業标準化技術協會的審定并發布。

該标準與UCIe主要有兩大(dà)區别:UCIe隻定義了并口,CCITA的Chiplet标準既定義了并口,也定義了串口,兩者的協議層自定義數據包格式也不同,但CCITA的标準與UCIe兼容,可直接使用已有生(shēng)态環境。在封裝層面,UCIe支持英特爾先進封裝、AMD封裝,CCITA定義的Chiplet标準主要采用國内可實現的封裝技術。