芯片的生産(chǎn)流程非常複雜,粗略來說,這一流程包括:制定規格、選擇構架、邏輯設計、電(diàn)路設計、布線(xiàn)、制造、測試、封裝(zhuāng)、總測試。這其中(zhōng)最重要的是電(diàn)路設計和制造,而芯片的制造工(gōng)藝最能(néng)體(tǐ)現一個公(gōng)司的技(jì )術水平。

在基爾比發明了芯片後的幾年裏,RCA開發出了MOS管。1962年,RCA在仙童的矽平面雙極工(gōng)藝的基礎上,開發出了MOS矽平面工(gōng)藝。與雙極型芯片相比,MOS芯片具(jù)有(yǒu)功耗低、結構簡單、集成度高、成品率高的優點。1963年,矽平面工(gōng)藝的CMOS芯片工(gōng)藝也被開發出來了,很(hěn)快,CMOS芯片工(gōng)藝就成了芯片産(chǎn)業的主流。今天,90%以上的芯片是由矽平面的CMOS芯片工(gōng)藝制造的。

從芯片的發展曆史來看,芯片的發展方向是高速、高頻、低功耗。因此,CMOS芯片成為(wèi)首選。目前,最先進的CMOS芯片工(gōng)藝制程已到了7納米,這相當于28個二氧化矽分(fēn)子的大小(xiǎo)。CMOS芯片的工(gōng)藝極為(wèi)複雜,使用(yòng)的設備動辄上億美元。但是,因為(wèi)芯片帶來的利潤非常大,很(hěn)多(duō)公(gōng)司和機構還是願意投資芯片制造業。

芯片工(gōng)藝四大流程

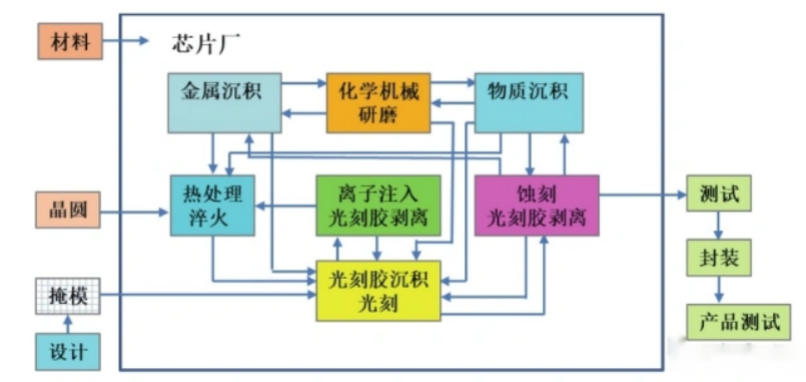

CMOS芯片工(gōng)藝流程可(kě)分(fēn)為(wèi)前端制造(包括晶圓處理(lǐ)、晶圓測試)和後段制造(包括封裝(zhuāng)、測試)。

晶圓處理(lǐ):是在矽晶圓上制作(zuò)電(diàn)子器件(如CMOS、電(diàn)容、邏輯閘等)與電(diàn)路,該過程極其複雜且投資極大,以微處理(lǐ)器為(wèi)例,其制造工(gōng)序可(kě)達數百道,所需加工(gōng)設備先進且昂貴,動辄上千萬美元一台。對制造環境無塵室(Clean-room)的要求極嚴苛,溫度、濕度與含塵均需嚴格控制。盡管,各類産(chǎn)品的制造工(gōng)序稍有(yǒu)不同,但基本工(gōng)序一般是在晶圓清洗後,進行氧化及澱積,然後反複進行光刻、刻蝕、薄膜澱積及離子注入等工(gōng)序,最後形成晶圓上的電(diàn)路。

晶圓測試:是在晶圓完成後,在晶圓上進行的電(diàn)測試。一般情形下,一片晶圓上隻有(yǒu)一種産(chǎn)品。每個晶粒将會一一經過測試,不合格的晶粒被标上記号。然後,晶圓将以晶粒為(wèi)單位切割成一粒粒獨立的晶粒。

芯片封裝(zhuāng):利用(yòng)塑料或陶瓷包裝(zhuāng)晶粒與配線(xiàn)以成産(chǎn)品;目的是給制造出的電(diàn)路加上保護層,避免電(diàn)路受到機械性刮傷或是高溫破壞。

最後測試:是對封裝(zhuāng)好的芯片進行測試,以保證其正品率即良率。

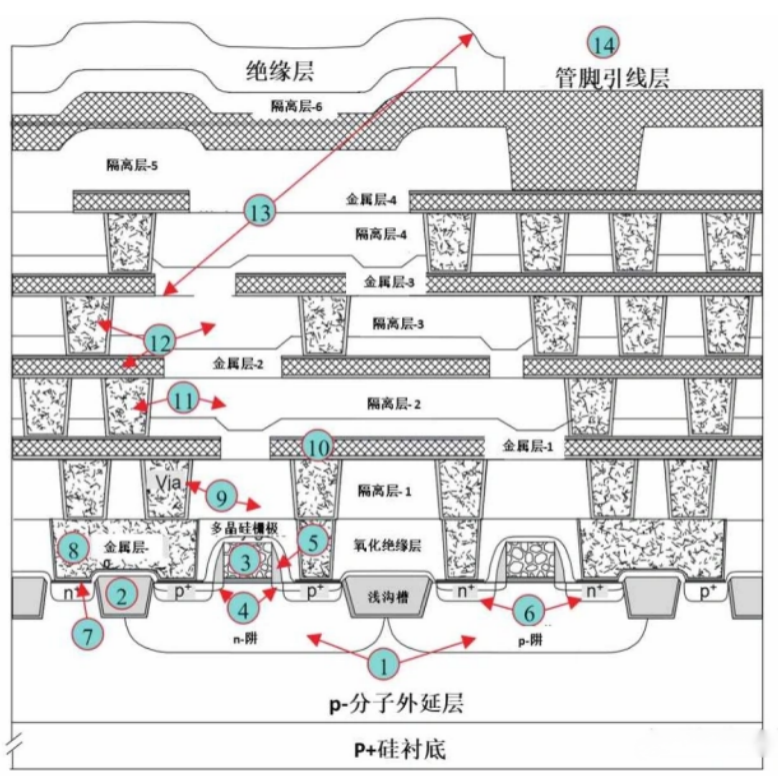

下圖是一張CMOS芯片的截面圖和對應的工(gōng)藝。

CMOS芯片的截面圖和對應的工(gōng)藝步驟

1—定義雙阱 2—定義隔離淺溝槽 3—定義栅極氧化層及栅極 4—定義源、漏的淺結 5—定義栅極氧化矽側牆 6—定義源、漏區(qū) 7—定義源、漏合金區(qū) 8—定義氧化層和源、漏連接金屬層0 9—定義隔離層1和金屬層0、1的連接 10—定義金屬層1 11—定義隔離層2和金屬層1、2的連接 12—定義隔離層3、金屬層2和金屬層2、3的連接 13—定義隔離層4、5金屬層3、4和它們的連接 14—定義管腳引線(xiàn)及外層絕緣

芯片制造六大步驟

芯片制造一般有(yǒu)六個重要步驟:一是光刻(Photolithography);二是離子注入(Ion Implantation);三是擴散(Diffusion);四是薄膜澱積(Deposition);五是刻蝕(Etch);六是化學(xué)機械研磨(Chemical Mechanical Polishing,CMP)。這六個步驟在芯片制造的過程中(zhōng)會被反複用(yòng)到,把各種不同的器件制作(zuò)在矽晶圓上,然後通過金屬沉積把做好的器件連接成電(diàn)路。

芯片制造流程

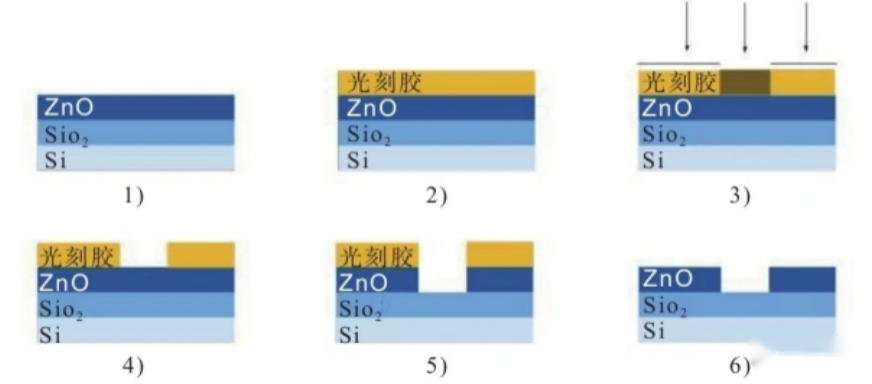

1. 光刻:光刻和傳統的照相相似,先在晶圓上塗上光刻膠(Photo Resistor),然後曝光掩膜闆(Mask),顯影光刻膠(Develop),再刻蝕曝光過的區(qū)域。于是,晶圓上就留出了刻蝕或離子注入的區(qū)域。光刻工(gōng)藝主要用(yòng)于定義矽晶圓上的幾何圖案(見圖14-3)。

光刻過程示意圖,1)需要被刻蝕的ZnO被澱積在SiO2/Si襯底上 2)塗膠 3)曝光 4)顯影 5)刻蝕 6)清洗-摘自《芯片改變世界》錢綱

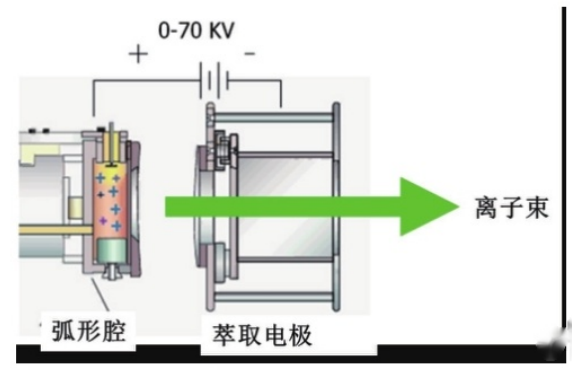

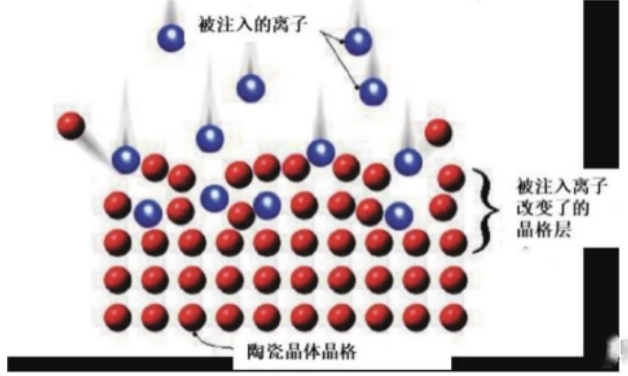

2. 離子注入。離子注入就是把晶圓作(zuò)為(wèi)一個電(diàn)極,在離子源和晶圓之間加上高電(diàn)壓,于是那些摻雜離子就會以極高的能(néng)量打入晶圓,在晶圓上形成N或P型區(qū)域。離子注入後必須對晶圓進行高溫退火(Anneal)從而修複離子注入後晶圓的損傷。離子注入主要用(yòng)于制造不同的半導體(tǐ)區(qū)域(N區(qū)或P區(qū)見下圖)。

離子注入過程示意圖

離子注入後矽晶圓的損傷

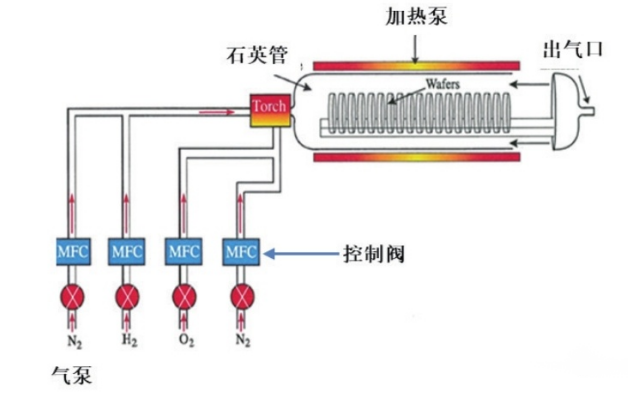

3. 擴散。擴散在芯片制造中(zhōng)有(yǒu)兩個作(zuò)用(yòng):一是在高溫下激活或把雜質(zhì)注入矽晶圓,二是産(chǎn)生氧化層,産(chǎn)生氧化層的溫度為(wèi)800~1050℃。

擴散設備示意圖

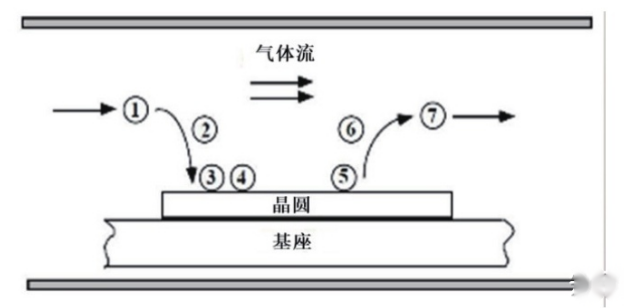

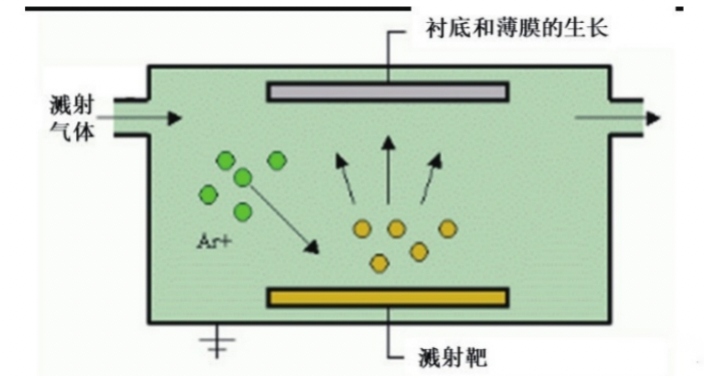

4. 薄膜澱積。薄膜澱積是把物(wù)質(zhì)沉積在晶圓表面上。有(yǒu)化學(xué)氣相澱積(Chemical Vapor Deposition,CVD)和物(wù)理(lǐ)氣相澱積(Physical Vapor Deposition,PVD)等方法。化學(xué)氣相澱積是把幾種氣體(tǐ)注入矽晶圓之上,進行化學(xué)反應後物(wù)質(zhì)澱積在晶圓上。物(wù)理(lǐ)氣相澱積把一個個原子澱積在矽晶圓上,它是從固相到氣相再到固相的過程。

化學(xué)氣相澱積(CVD)示意圖

物(wù)理(lǐ)氣相澱積(PVD)示意圖

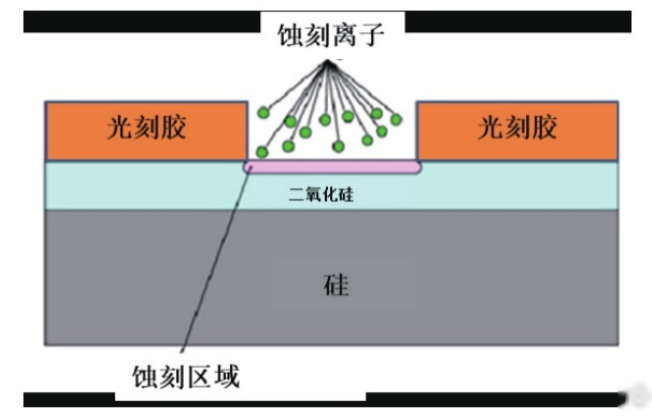

6. 刻蝕。刻蝕是按照掩模圖形或設計要求對半導體(tǐ)襯底(Substrate)表面或表面覆蓋薄膜進行選擇性腐蝕或剝離。刻蝕有(yǒu)濕刻蝕(Wet Etch)和等離子刻蝕(Plasma Etch)兩種。濕刻蝕是把矽晶圓浸入某種化學(xué)溶液中(zhōng),把要去掉的物(wù)質(zhì)腐蝕掉。等離子刻蝕則是用(yòng)高能(néng)等離子束把要去掉的物(wù)質(zhì)打掉。

離子刻蝕過程示意圖

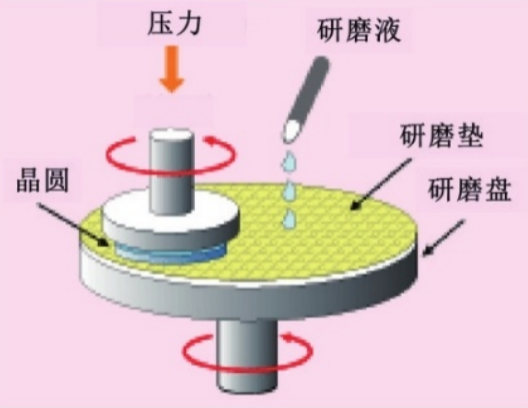

6. 化學(xué)機械研磨。為(wèi)了使矽晶圓的表面在經過加工(gōng)後仍然平坦,就要對加工(gōng)後的矽晶圓表面進行研磨。

化學(xué)機械研磨(CMP)過程示意圖

工(gōng)作(zuò)中(zhōng)的化學(xué)機械研磨設備

--摘自《芯片改變世界》錢綱